Counter Circuits

Counting in Binary

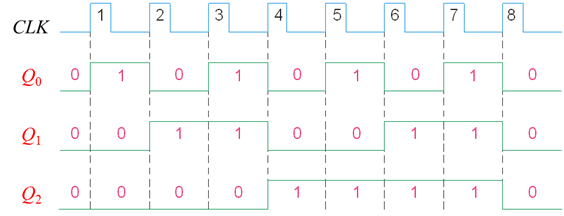

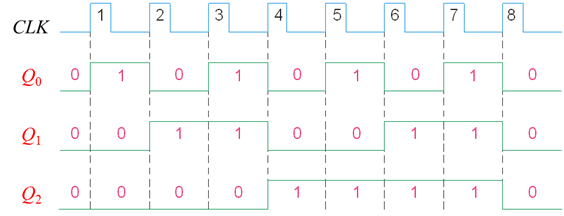

- As you know, the binary count sequence follows a familiar pattern of 0's and 1's

- LSB changes on every number.

- The next bit changes on every other number.

- The next bit changes on every fourth number.

A counter can form the same pattern of 0's and 1's with logic levels. The first stage in the counter represents the least significant bit – notice that these waveforms follow the same pattern as counting in binary.

Analysis of Sequential Circuits

- Sequential logic circuits follow a predetermined sequence of digital states and are triggered by timing pulses or clock.

- Most sequential logic can best be analyzed using timing diagrams.

- The timing analysis can be done by observing the level on the D or J-K inputs prior to the clock.

- Asynchronous inputs (set and reset) must be considered separately.

Ripple Counters

- A counter circuit can be built by cascading flip-flops together. (Connecting the Q output of one flip-flop to the clock input of the next)

- The number of states in a counter (modulus) is 2N where N is the number of flip-flops.

- In order for a counter to operate properly each flip-flop must toggle. For J-K flip-flops this means both J and K must be high.

- In a ripple counter the clock input has to propagate through each flip-flop of the counter.

- A ripple counter is also called an asynchronous counter because each flip-flop does not change at the same time.

- The propagation delay of each flip-flop adds together to give a total propagation delay for the counter. This propagation delay will limit the maximum frequency allowed by the input trigger clock.

- A down counter can be formed by taking the output from the

output instead of the Q output of each flip-flop.

output instead of the Q output of each flip-flop.

- In an asynchronous counter, the clock is applied only to the first stage. Subsequent stages derive the clock from the previous stage.

- The three-bit asynchronous counter shown is typical. It uses J-K flip-flops in the toggle mode.

Design of Divide-by-N Counters

- A counter can also be used as a frequency divider.

- Each flip-flop will divide its input signal by 2 such that the output of the last stage will be a frequency equal to the input frequency divided by the Modulus number.

- A counter with any Modulus number can be formed by using an external gate to reset the counter at a predetermined number.

- The logic gate is used to decode the binary equivalent of the MOD number. For a MOD-5 counter, the NAND gate must decode state 101.

- The decoder can be used to preset some of the flip-flops as well as reset the flip-flops. This means that the count sequence will start at some state other then zero.

- An enable gate (2-input AND gate) can be used to stop a counter when its final state is reached.

Ripple Counter Integrated Circuits

- The 7493 is a four-bit ripple counter with a common reset.

- The 7493 can be used as a MOD-2, a MOD-8 or a MOD-16 counter without the reset.

- By using the reset inputs, the 7493 can be configured in any Modulo number up to 16.

- The 7490 is a four-bit ripple counter that has a divide-by-2 section and a divide-by-5 section.

- The 7490 is most commonly used as a decade counter (MOD-10) with reset inputs and set inputs that force the counter to state 9.

- The 7492 is a four-bit ripple counter that has a divide-by-2 section and a divided-by-6 section.

- The 7492 is most commonly used as a MOD-6 or a MOD-12 counter.

System Design Applications

- The IC counters can be cascaded together to get larger MOD numbers.

- Any special state of a counter can be decoded to light an LED, sound a buzzer, operate a relay or any other external function.

- Several 7490s can be cascaded together to form BCD counters.

Seven-Segment LED Display Decoders

- A BCD counter can count through the decimal digits 0 through 9.

- A seven-segment LED display can be used to display the decimal digits 0–9.

- Each segment of the LED display is an LED and when certain segments are lit the 10 decimal digits will be displayed (see Figure 12-4 of the textbook).

- A special decoder is necessary to convert the binary output of the counter to the proper code to activate the required LED segments.

- A common-anode LED display requires an active-LOW decoder output.

- The 7447 IC is an active-LOW output BCD-to-seven-segment decoder/driver.

- The 7447 also has a lamp test input and a ripple blanking input and output.

- DIP ICs are available with resistor networks and can make the wiring of counter displays much easier.

Synchronous Counters

- A synchronous counter eliminates the accumulated propagation delay of the ripple counter by tying all clock inputs to a common clock signal.

- In a synchronous counter each flip-flop must not be allowed to toggle until all flip-flops that precede it are high (set).

- The J-K inputs are tied to an AND gate that ANDs the Q outputs from all previous flip-flops.

- Synchronous counters can be used to form any modulus counter by using a NAND gate to reset all the flip-flops. The inputs to the logic gate are from the Q outputs of the flip-flops that form the binary representation of the MOD numbers.

- Synchronous counters can be used as down counters by taking the output from the

rather than the Q of each flip-flop.

rather than the Q of each flip-flop.

- Synchronous counters can be used in many of the same design applications as ripple counters.

Synchronous Up/Down-Counter ICs

- The 74192 is a BCD decade up/down synchronous counter.

- The 74193 is a 4-bit binary up/down synchronous counter.

- These chips also have parallel data input leads that can be used to preset the counter.

- Two clock inputs are available; one for an UP count and the other for a DOWN count.

- A terminal count UP and a terminal count DOWN output signal can be used to cascade several ICs together.

- Two additional synchronous IC counters are the 74190 and the 74191.

- The 74190 is a BCD counter and the 74191 is a 4-bit binary counter.

- These chips have a terminal count output and an enable input. With these two connections, cascaded ICs held-off until the proper count. This means that the entire counter can be synchronous.

Applications of Synchronous Counter ICs

- The UP/DOWN counter can be used as a self-reversing counter.

- The parallel load feature can be used to preset the counter for some initial count.

Additional Notes

Any or all states of a counter can be decoded using AND gates. One is required for each state of the counter to be decoded. AND gate decoders will produce active-HIGH outputs and NAND gate decoders will produce active-LOW outputs. If a ripple counter is decoded, the glitches can appear in the decoder outputs. These glitches are unwanted counter states and are caused by the propagation delay of the flip-flops. Not all the flip-flops will change state at the same time causing the decoder to detect states that are not in the correct sequence.

There are several ways to correct these decoder glitches. One way is to strobe the decoder; that is, to enable the decoder only during the middle of the clock pulse used to toggle the counter. This will avoid the propagation delay time and prevent the glitches. Another approach is the use of a synchronous counter. In the synchronous counter all flip-flops change state at the same time. When all flip-flops are toggled from the same clock there is no overlap of the flip-flop action and as a result no glitches in the decoder.