Integrated-Circuit J-K Flip-Flop (7476, 74LS76)

- The 7476 is a master—slave J-K and the 74LS76 is a negative edge-triggered J-K flip-flop.

- Both chips have the same pin configuration.

- Both chips have synchronous inputs of J, K and Cp.

- Both chips have asynchronous inputs.

- The J-K flip-flop can be made into a D flip-flop by bringing the data input into the J and the inverse of the data input into the K input.

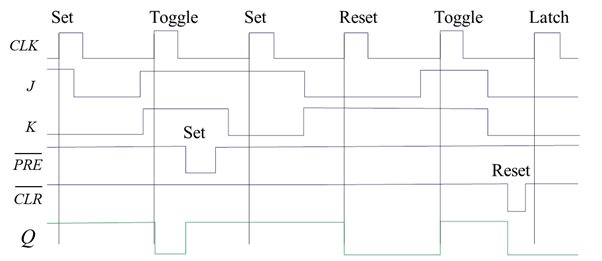

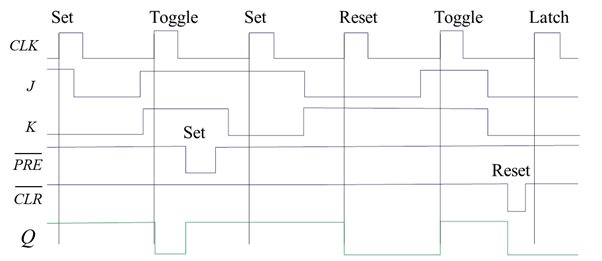

- Synchronous inputs are transferred in the triggering edge of the clock (for example the D or J-K inputs). Most flip-flops have other inputs that are asynchronous, meaning they affect the output independent of the clock.

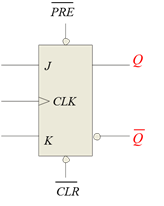

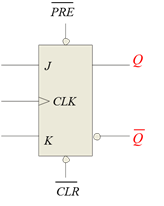

- Two such inputs are normally labeled preset (PRE) and clear (CLR). These inputs are usually active LOW. A J-K flip flop with active LOW preset and CLR is shown.

return to top | previous page | next page